# A Novel Approach for VHDL Implementation of Universal Line Encoder for Communication

## Prabhat Kumar Mishra<sup>1</sup> and Sahaj Saxena<sup>2</sup>

<sup>1</sup>Department of Electronics and Communication, DJCET, Modinagar, India, E-mail: prabhat\_viet@hotmail.com. <sup>2</sup>Department of Control and System, IIT Roorkee, India, E-mail: mrsahajsaxena@hotmail.com.

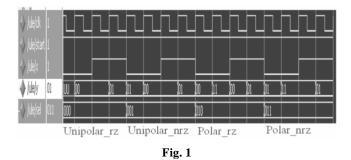

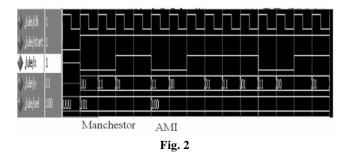

*Abstract:* This paper describes the implementation of various line coding schemes using VHDL on a single chip and enables the user to select one of them for the purpose of security, area optimization and can support communication in varying channel environment. The choice of line code depends upon presence or absence of DC level, power spectral density, bandwidth, BER performance, ease of clock signal recovery and presence or absence of inherent error detection property. The line encoding schemes used are Unipolar RZ and NRZ, Polar RZ and NRZ, AMI and Manchestor codings. Select pin impinged on the chip enables the users to select any one of the line encoding technique according to their requirement. The waveforms of Universal Line Encoder are presented using Modelsim 6.4.

Keywords: AMI (Alternate Mark Inversion), Line Encoding, NRZ (Non Return to Zero).

## 1. INTRODUCTION

After the emergence of VLSI technology, researchers are continuously trying to implement various algorithms by using VHDL or Verilog<sup>1-9</sup> but power, area optimization and reduction of time delay are big challenges in front of engineers<sup>10</sup>. Line encoding is key building block of communication system in which binary 1's and 0's are translated into a sequence of voltage pulses that can be propagated over wire<sup>11</sup>. Digital baseband signals often use line codes to provide particular spectral characteristic of a pulse train. Most popular codes are return to zero and non return to zero. All of these may be either unipolar, polar or bipolar. The choice of line code depends upon presence or absence of DC level, power spectral density, bandwidth, BER performance, ease of clock signal recovery and presence or absence of inherent error detection property<sup>12</sup>. RZ implies that pulse return to zero within every bit period. This leads to spectral widening but improves timing synchronization. NRZ codes, on the other hand do not return to zero in a bit period—the signal stays at constant level throughout a bit period. NRZ codes are more spectrally efficient than RZ codes, but offer poorer synchronization capabilities<sup>13</sup>. Unipolar encoding is inexpensive to implement but its average amplitude is nonzero, this creates a direct current (DC) component. Average DC value is minimum in polar formats as well as there is no signal droop<sup>14</sup> but they are not transparent. Manchestor codes are self synchronizing but they have no error detection capability, so are not suitable for wide area network.

#### 2. ALGORITHM

Signed binary notation is used to implement this design as explained in table (A and B). Xilinx Project Navigator is used to implement this design<sup>15</sup>.

| Tabl | le A |

|------|------|

|------|------|

| Line encoding<br>technique | Input<br>(x) | Output (y) $(0 - T_b/2)$ | $Output(y)  (T_b/2 - Tb)$ |

|----------------------------|--------------|--------------------------|---------------------------|

| Unipolar-RZ                | 0            | 00                       | 00                        |

|                            | 1            | 01                       | 00                        |

| Unipolar_NRZ               | 0            | 00                       | 00                        |

|                            | 1            | 01                       | 01                        |

| Polar_RZ                   | 0            | 11                       | 00                        |

|                            | 1            | 01                       | 00                        |

| Polar_NRZ                  | 0            | 11                       | 11                        |

|                            | 1            | 01                       | 01                        |

| Manchestor                 | 0            | 11                       | 01                        |

|                            | 1            | 01                       | 11                        |

Table B Truth Table for AMI

| Present state | Input (x) | Output $(y_0 y_1)$ | Next state |

|---------------|-----------|--------------------|------------|

| 0             | 0         | 00                 | 0          |

| 0             | 1         | 01                 | 1          |

| 1             | 0         | 00                 | 1          |

| 1             | 1         | 11                 | 1          |

SOLID CONVERTER PDF

#### 3. MODELSIM SIMULATION RESULT

Modelsim 6.4 is used to see the waveforms of the project as shown in Figs (1 and 2). In this model select pin is used to change line encoding technique. In these waveforms the delay of 1 clock is observed.

#### 4. CONCLUSION

The waveforms of Universal Line Encoder are presented using Modelsim 5.4 and confirm very well to the theoretical findings. Thus Universal Line Encoder can be built on a single chip enabling the user to select any of the line code schemes thereby eliminating each single chip for each code scheme. This technology is secure, compact in size and channel efficient. The procedure involved to build this encoder ease the test application processes and allow high level control for communication. The approach to develop algorithm for universal line encoder is quite simple and suitable for testing real life applications in communication.

### REFERENCES

D. Boolchandani, A. Mundra, S. Chelawat, S. Das and P. Agarwal, "DManav: An Electronic Device for Unmanned

SOLID CONVERTER

Railway Crossing", *IETE Journal of Education*, **49** (**3**), Sept.-Dec. 2008, pp. 8994.

- [2] Valentina Salapura, Volker Hamann, "Implementing Fuzzy Control System using VHDL and State Chart", *IEEE xplore*, 1996.

- [3] C.K. Chuang, C.G. Harrison, "Analogue Behavioural Modeling and Simulation using VHDL and Saber-mast", *IEEE xplore*, 1994.

- [4] Charles P. Brothers jr., Mark A. Mehalik, "Rapid and Accurate Timing Simulation of Radiation Hardened Digital Microelectronics using VHDL", *IEEE xplore*.

- [5] Mamum Bin Ibne Reaz, Md. Shabieul Islam, Md. S. Sulaiman, "Pipeline Floating Point ALU Design using VHDL", *ICSE2002 Proc. 2002*, Penang, Malaysia.

- [6] Mamum Bin Ibne Reaz, Md. Shabieul Islam, Md. S. Sulaiman, "A Single Clock Cycle MIPS RISC Processor Design using VHDL", *ICSE2002 Proc. 2002*, Penang, Malaysia.

- [7] P. Sankar, "Implementation of DSR Algorithm using VHDL in Wireless Ad-hoc Network", *IEEE xplore*, 2004.

- [8] M. Habib Ullah, A. Unggul Priantoro, M. Asaraful Hasan, M. Jasim Uddin, "FPGA Implementation of Light Rail Transit Fare Card Controller using VHDL", *European Journal of Scientific Research*, **36** (1), (2009), pp. 30–40.

- [9] Prabhat K. Mishra, Dheeraj Sinha, Deepa Singh, Jaya Yadav, "Digital Modulation Unit for Decimal Integers using VHDL", project report submitted to deptt. of ET, VIET, G. B. Nagar.

- [10] Prabhat K. Mishra, Sahaj Saxena, "Automation Need to Meet New Product Challenges", Wisdom Journal of Vishveshwarya School of Buisiness Management, 1 (2), December 2009.

- [11] Behrouz A. Forouzan, "Data Communication and Networking". Second edition, Tata McGraw-Hill, 2003.

- [12] Simon Haykin, "Comunication System". Fourth edition.

- [13] Theodore S. Rappaport, "Wireless Communication: Principles and Practice". Second edition, Pearson Education, Prentice Hall, 2002.

- [14] B.P. Lathi, "Modern Digital and Analog Communications". Third edition.

- [15] J. Bhaskar, "A VHDL Primer". Third edition, Pearson Education, Prentice Hall, 2008.

PDF

To remove this message, purchase the

product at www.SolidDocuments.com